Учебник CSS

Невозможно отучить людей изучать самые ненужные предметы.

Введение в CSS

Преимущества стилей

Добавления стилей

Типы носителей

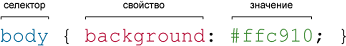

Базовый синтаксис

Значения стилевых свойств

Селекторы тегов

Классы

CSS3

Надо знать обо всем понемножку, но все о немногом.

Идентификаторы

Контекстные селекторы

Соседние селекторы

Дочерние селекторы

Селекторы атрибутов

Универсальный селектор

Псевдоклассы

Псевдоэлементы

Кто умеет, тот делает. Кто не умеет, тот учит. Кто не умеет учить - становится деканом. (Т. Мартин)

Группирование

Наследование

Каскадирование

Валидация

Идентификаторы и классы

Написание эффективного кода

Самоучитель CSS

Вёрстка

Изображения

Текст

Цвет

Линии и рамки

Углы

Списки

Ссылки

Дизайны сайтов

Формы

Таблицы

CSS3

HTML5

Новости

Блог для вебмастеров

Новости мира Интернет

Сайтостроение

Ремонт и советы

Все новости

Справочник CSS

Справочник от А до Я

HTML, CSS, JavaScript

Афоризмы

Афоризмы о учёбе

Статьи об афоризмах

Все Афоризмы

| Помогли мы вам |

TSMC и Broadcom представили чип с подложкой-мостом с вдвое увеличенной площадью - «Новости сети»

Информация размещенная на сайте - «hs-design.ru»

- © TSMC внедряет настоящую 3D-упаковку полупроводников - «Новости сети»

- © TSMC собирается строить новый завод для 3D-упаковки чипов - «Новости сети»

- © Услуги по трёхмерной компоновке TSMC сделает своим самым динамично растущим бизнесом - «Новости сети»

- © TSMC построит новую фабрику для 5-нм и 3-нм производства - «Новости сети»

- © TSMC подтвердила планы массового производства 3-нм чипов в 2022 году - «Новости сети»

- © TSMC готовится к производству 10-нм процессоров Apple A11 - «Новости сети»

- © Слухи: TSMC уже печатает 7-нм чипы A11X для iPad Pro - «Новости сети»

- © TSMC готовится к массовому производству чипов по 12-нм технологии FinFET - «Новости сети»

- © TSMC может получить заказы Qualcomm на производство 7-нм чипов Snapdragon - «Новости сети»

- © TSMC начнёт пробный выпуск 7-нм изделий через год - «Новости сети»

|

|

|