Учебник CSS

Невозможно отучить людей изучать самые ненужные предметы.

Введение в CSS

Преимущества стилей

Добавления стилей

Типы носителей

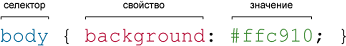

Базовый синтаксис

Значения стилевых свойств

Селекторы тегов

Классы

CSS3

Надо знать обо всем понемножку, но все о немногом.

Идентификаторы

Контекстные селекторы

Соседние селекторы

Дочерние селекторы

Селекторы атрибутов

Универсальный селектор

Псевдоклассы

Псевдоэлементы

Кто умеет, тот делает. Кто не умеет, тот учит. Кто не умеет учить - становится деканом. (Т. Мартин)

Группирование

Наследование

Каскадирование

Валидация

Идентификаторы и классы

Написание эффективного кода

Самоучитель CSS

Вёрстка

Изображения

Текст

Цвет

Линии и рамки

Углы

Списки

Ссылки

Дизайны сайтов

Формы

Таблицы

CSS3

HTML5

Новости

Блог для вебмастеров

Новости мира Интернет

Сайтостроение

Ремонт и советы

Все новости

Справочник CSS

Справочник от А до Я

HTML, CSS, JavaScript

Афоризмы

Афоризмы о учёбе

Статьи об афоризмах

Все Афоризмы

| Помогли мы вам |

Cadence и Imec создают проект 3-нм 64-битного процессора - «Новости сети»

Информация размещенная на сайте - «hs-design.ru»

Информация размещенная на сайте - «hs-design.ru»

- © imec открывает новую «чистую комнату» для освоения техпроцессов с нормами менее 7 нм - «Новости сети»

- © IMEC разработает техпроцесс для производства ReRAM компании 4DS - «Новости сети»

- © Производство с нормами 5 нм и сканерами EUV может быть отложено - «Новости сети»

- © GlobalFoundries представила пакет инструментов для проектирования 7-нм чипов - «Новости сети»

- © Samsung обещает начать выпуск 4-нм чипов в 2020 году - «Новости сети»

- © Китайский производитель получил от властей деньги на новые техпроцессы - «Новости сети»

- © Прогрессивная упаковка процессора Apple A10 поможет создать тончайший смартфон - «Новости сети»

- © GlobalFoundries начала поставки прототипов радиочипов для сетей 5G - «Новости сети»

- © TSMC построит завод по выпуску 3-нанометровых изделий - «Новости сети»

- © ASML отмечает высокий спрос на сканеры EUV - «Новости сети»

|

|

|