Учебник CSS

Невозможно отучить людей изучать самые ненужные предметы.

Введение в CSS

Преимущества стилей

Добавления стилей

Типы носителей

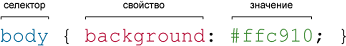

Базовый синтаксис

Значения стилевых свойств

Селекторы тегов

Классы

CSS3

Надо знать обо всем понемножку, но все о немногом.

Идентификаторы

Контекстные селекторы

Соседние селекторы

Дочерние селекторы

Селекторы атрибутов

Универсальный селектор

Псевдоклассы

Псевдоэлементы

Кто умеет, тот делает. Кто не умеет, тот учит. Кто не умеет учить - становится деканом. (Т. Мартин)

Группирование

Наследование

Каскадирование

Валидация

Идентификаторы и классы

Написание эффективного кода

Самоучитель CSS

Вёрстка

Изображения

Текст

Цвет

Линии и рамки

Углы

Списки

Ссылки

Дизайны сайтов

Формы

Таблицы

CSS3

HTML5

Новости

Блог для вебмастеров

Новости мира Интернет

Сайтостроение

Ремонт и советы

Все новости

Справочник CSS

Справочник от А до Я

HTML, CSS, JavaScript

Афоризмы

Афоризмы о учёбе

Статьи об афоризмах

Все Афоризмы

| Помогли мы вам |

Нужен самый быстрый интерфейс для памяти HBM2E? Обращайтесь в Synopsys - «Новости сети»

Информация размещенная на сайте - «hs-design.ru»

- © Samsung начнёт выпускать самую быструю память HBM2E в текущем полугодии - «Новости сети»

- © В семействе Intel Arctic Sound будут видеокарты с уровнем TDP до 500 Вт - «Новости сети»

- © Дискретное графическое решение Arctic Sound будет многопроцессорным - «Новости сети»

- © Документация SK Hynix упоминает возможные характеристики флагманского AMD Navi - «Новости сети»

- © Проведена первая в мире демонстрация возможностей интерфейса USB 3.2 - «Новости сети»

- © Сервис для поиска багов в коде, Coverity Scan, не работал из-за заражения майнером - «Новости»

- © Опубликована спецификация стандарта USB 3.2 - «Новости сети»

- © Карточек памяти стало больше: представлены карты памяти UFS - «Новости сети»

- © Samsung начала выпуск 8-Гбайт памяти HBM2 с наивысшей скоростью обмена - «Новости сети»

- © В разгоне память Micron GDDR6 может работать на 20 Гбит/с - «Новости сети»

|

|

|