Учебник CSS

Невозможно отучить людей изучать самые ненужные предметы.

Введение в CSS

Преимущества стилей

Добавления стилей

Типы носителей

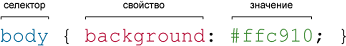

Базовый синтаксис

Значения стилевых свойств

Селекторы тегов

Классы

CSS3

Надо знать обо всем понемножку, но все о немногом.

Идентификаторы

Контекстные селекторы

Соседние селекторы

Дочерние селекторы

Селекторы атрибутов

Универсальный селектор

Псевдоклассы

Псевдоэлементы

Кто умеет, тот делает. Кто не умеет, тот учит. Кто не умеет учить - становится деканом. (Т. Мартин)

Группирование

Наследование

Каскадирование

Валидация

Идентификаторы и классы

Написание эффективного кода

Самоучитель CSS

Вёрстка

Изображения

Текст

Цвет

Линии и рамки

Углы

Списки

Ссылки

Дизайны сайтов

Формы

Таблицы

CSS3

HTML5

Новости

Блог для вебмастеров

Новости мира Интернет

Сайтостроение

Ремонт и советы

Все новости

Справочник CSS

Справочник от А до Я

HTML, CSS, JavaScript

Афоризмы

Афоризмы о учёбе

Статьи об афоризмах

Все Афоризмы

| Помогли мы вам |

Характеристики иженерных образцов EPYC Milan вселяют оптимизм по поводу частот Zen 3 - «Новости сети»

- © Монолитные кристаллы AMD EPYC обходились бы в два раза дороже чиплетов - «Новости сети»

- © Рискованный разгон инженерных образцов EPYC Rome обеспечил абсолютный рекорд в Corona - «Новости сети»

- © Процессоры Ice Lake-SP могут превзойти предшественников по быстродействию в два раза - «Новости сети»

- © В следующем году будет создан суперкомпьютер с 128-ядерными процессорами AMD Milan - «Новости сети»

- © Процессоры AMD с архитектурой Zen 3 увеличат производительность максимум на 15 % - «Новости сети»

- © Новые тесты AMD EPYC Rome: рост производительности налицо - «Новости сети»

- © Появились свидетельства подготовки многоядерных Intel Ice Lake для рабочих станций - «Новости сети»

- © Раскрыта конфигурация процессора Snapdragon 8150 - «Новости сети»

- © Архитектура AMD Zen 3 предложит до четырёх потоков на одно ядро - «Новости сети»

- © AMD за год увеличила объёмы поставок процессор EPYC в три раза - «Новости сети»

|

|

|