Учебник CSS

Невозможно отучить людей изучать самые ненужные предметы.

Введение в CSS

Преимущества стилей

Добавления стилей

Типы носителей

Базовый синтаксис

Значения стилевых свойств

Селекторы тегов

Классы

CSS3

Надо знать обо всем понемножку, но все о немногом.

Идентификаторы

Контекстные селекторы

Соседние селекторы

Дочерние селекторы

Селекторы атрибутов

Универсальный селектор

Псевдоклассы

Псевдоэлементы

Кто умеет, тот делает. Кто не умеет, тот учит. Кто не умеет учить - становится деканом. (Т. Мартин)

Группирование

Наследование

Каскадирование

Валидация

Идентификаторы и классы

Написание эффективного кода

Самоучитель CSS

Вёрстка

Изображения

Текст

Цвет

Линии и рамки

Углы

Списки

Ссылки

Дизайны сайтов

Формы

Таблицы

CSS3

HTML5

Новости

Блог для вебмастеров

Новости мира Интернет

Сайтостроение

Ремонт и советы

Все новости

Справочник CSS

Справочник от А до Я

HTML, CSS, JavaScript

Афоризмы

Афоризмы о учёбе

Статьи об афоризмах

Все Афоризмы

| Помогли мы вам |

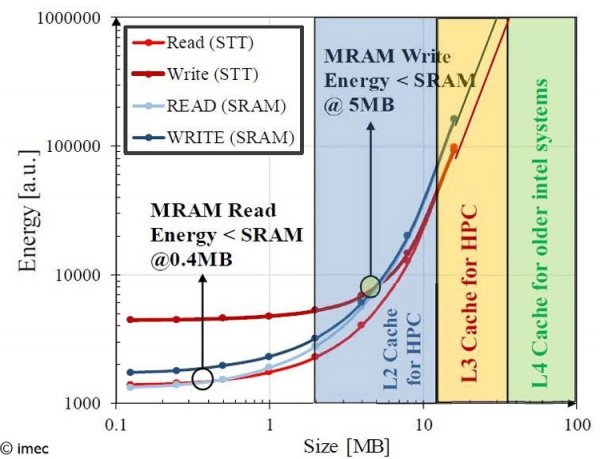

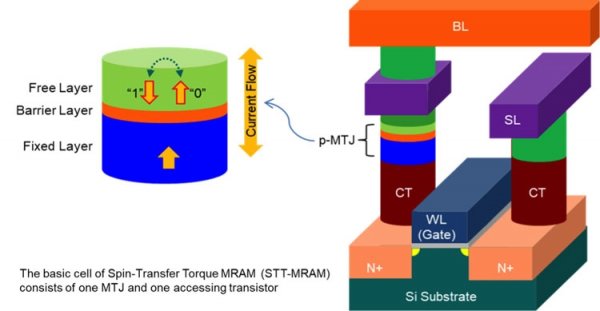

Imec доказал эффективность памяти SST-MRAM для разделяемой кеш-памяти - «Новости сети»

- © Кое-что новенькое: память SOT-MRAM можно выпускать в промышленных масштабах - «Новости сети»

- © В России появится производство магниторезистивной памяти STT-MRAM - «Новости сети»

- © UMC получает доступ к технологиям производства встраиваемой памяти MRAM - «Новости сети»

- © Магниторезистивную память Everspin договорились выпускать в Малайзии - «Новости сети»

- © Samsung первой приблизилась к выпуску 28-нм eMRAM на подложках FD-SOI - «Новости сети»

- © TSMC займётся производством микрочипов памяти eMRAM и eRRAM - «Новости сети»

- © Samsung обошла Intel по технологичности производства массивов SRAM - «Новости сети»

- © IMEC разработает техпроцесс для производства ReRAM компании 4DS - «Новости сети»

- © Cadence и Imec создают проект 3-нм 64-битного процессора - «Новости сети»

- © Imec представил технологию, которая вдвое увеличит плотность размещения транзисторов - «Новости сети»

|

|

|